## AN-6611 Binary/BCD Gain Programmed Amplifiers

Many systems require logic controlled Gain Programmable Amplifiers (GPA) for signal preconditioning, level control and dynamic range expansion. The system sets GPA requirements for accuracy, speed and signal handling capability, limiting the type used. Conventional CMOS analog switches limit signal handling to  $\pm 7.5$  V and accuracy to 1%. High voltage CMOS or JFET analog switches increase both accuracy and signal handling ( $\pm 10$  V to  $\pm 15$  V) but at a greater cost. Programmable amplifiers using current mode analog switches have the highest signal handling capability ( $\pm 25$  V) with high accuracy, speed and low cost.

In reality, the logic controlled GPA is a multiplying digitalto-analog converter (multiplying D/A). The D/A input is the reference node which is multiplied by the digital input. Multiplying D/A converters have been available for some time in module, hybrid and monolithic form but suffer from high cost and poor signal handling capability ( $\pm 10$  V maximum).

Large signal handling ( $\pm 25$  V), moderate cost multiplying D/A converters can be built using monolithic current mode analog switches, an op amp and a few resistors.

Unlike conventional analog switches, only signal current is switched at the virtual ground of an op amp with current mode analog switches. Limiting the voltage across the switch to a few hundred millivolts, power supplies, logic interface and level translator circuits are eliminated allowing the JFET switches to be driven directly by standard logic.

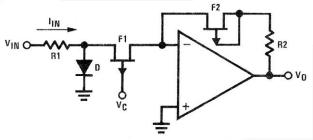

Figure 1. Current Mode Analog Switch

A logic "0" turns the switch ON with a logic "1" shutting the switch OFF by pinching the JFET OFF. The diode is used to clamp the source to drain voltage to about 0.7 V in the switch OFF state. The series JFET in the feedback path is used to compensate for the ON resistance of the switch JFET.

Current through the switch is determined by the input resistor, R1, the switch ON resistance and the input voltage,  $V_{IN}$ . Scaling of the output voltage is accomplished with the feedback resistor, setting the gain of the amplifier.

$$A_{V} = -\frac{R^2 + R_{ON2}}{R^1 + R_{ON1}}$$

(1)

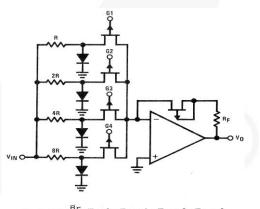

A 4-bit multiplying D/A converter can be built using a quad current mode switch, 4 binary weighted resistors (R, 2R, 4R, and 8R) and an op amp. The output voltage will be a function of the feedback resistor, input resistors and the logic state of the JFET gates,  $G_N$ .

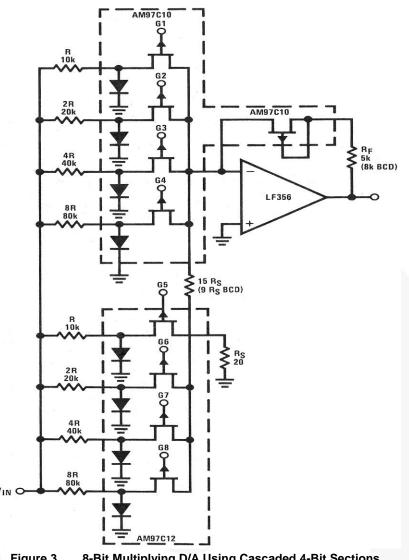

The number of bits is expanded by cascading another quad current switch and resistor array to the first. Instead of continuing the binary progression of the input resistors, (16R, 32R, etc), current splitting resistors are used such that the same resistor array (R, 2R, 4R, 8R) is used for the additional bits, minimizing the number of resistor values required for higher order converters.

$v_{O} = -v_{IN} \frac{R_F}{R} (\overline{G}_{1\ 2}^{0} + \overline{G}_{2\ 2}^{-1} + \overline{G}_{3\ 2}^{-2} + \overline{G}_{4\ 2}^{-3})$ Figure 2. 4-Bit Multiplying D/A Converter

8-Bit Multiplying D/A Using Cascaded 4-Bit Sections Figure 3.

Binary weighting requires a 1/16 current split for the second switch quad while BCD weighting requires a 1/10 split.

There are two basic switch configurations available that are optimized for a variety of logic drives: TTL or CMOS Multiple independent switches (four by SPST) and a four channel multiplex version with a series compensation JFET.

Practical limitations in using monolithic current mode analog switches need consideration. Resistor values and tolerance impacted by switch resistance is minimized by increasing resistor values without regard, but limits bandwidth and creates leakage errors at elevated temperatures. Using resistors that are too small, increases switch resistance errors. Current saturation (increased switch resistance) occurs when the switch current approaches the JFET saturation current, I<sub>DSS</sub>. High currents also cause  $I_G(ON)$ , current lost through the gate, as the diode and JFET source to gate diode become forward biased. An input resistor value of 10 k limits the switch current to less than 2 mA minimizing both leakage and switch resistance problems. For example, the gain accuracy at unity gain using the compensation JFET is less than 0.05% with R = RF = 10 k.

The current shunt resistor used in cascading switches should be kept small to minimize the voltage drop, keeping the JFET drains near ground. Values of R<sub>s</sub> should be less than 100 Ω (20 typical).

Resistor tolerance will be determined by converter resolution, i.e., the number if bits (N). For example, an 8-bit binary D/A converter will have 2<sup>N</sup>-1 or 255 steps (99 for BCD) or different gains. The resolution or smallest step is (least significant bit)  $1/2^{N}$  of the full-scale value (0.0039). Typical accuracy specifications for D/A converters are stated as 1 LSB or  $\pm 1/2$  LSB.

This works out to be  $\pm 0.2\%$  for the 8-bit binary unit. Errors in the feedback resistor directly affect the output of the converter. The most significant resistor, R, contributes 1/2 full-scale, reducing its error contribution by a factor of 2. The same is true for the rest of the resistors with

## AN-6611

contributions of 1/4, 1/8, etc. Using a resistor tolerance of 0.1% for the feedback resistor, 0.2% for the 2 most significant resistors (R, 2R), 0.5% for the 3rd and 1% for the 4th and 5th switches allows 5% resistors to be used in the 6th, 7th and 8th switch positions.

Using the above information, 4-bit or more binary/BCD gain programmable amplifiers can be built with large signal handling capability, few parts and easily adjustable gain or attenuation. Figure 3 shows a practical 8-bit binary/BCD GPA with gains of 0.996 (binary) with  $R_F = 5$  k and 0.99 (BCD) with RF = 8 k. For other gains, only the feedback resistor need be changed.

= tolerance of feedback resistor

$\epsilon_{R}$  = tolerance of most significant resistor

$\epsilon_{nR}$  = tolerance of Nth resistor

Author: John Maxwell, Feb 1977

## DISCLAIMER

FAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY PRODUCTS HEREIN TO IMPROVE RELIABILITY, FUNCTION, OR DESIGN. FAIRCHILD DOES NOT ASSUME ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN; NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS.

## LIFE SUPPORT POLICY

FAIRCHILD'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD SEMICONDUCTOR CORPORATION. As used herein:

- 1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, or (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in significant injury to the user.

- 2. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.