# SONY

# CXA2150AQ

## **CRT DRIVER**

#### Description

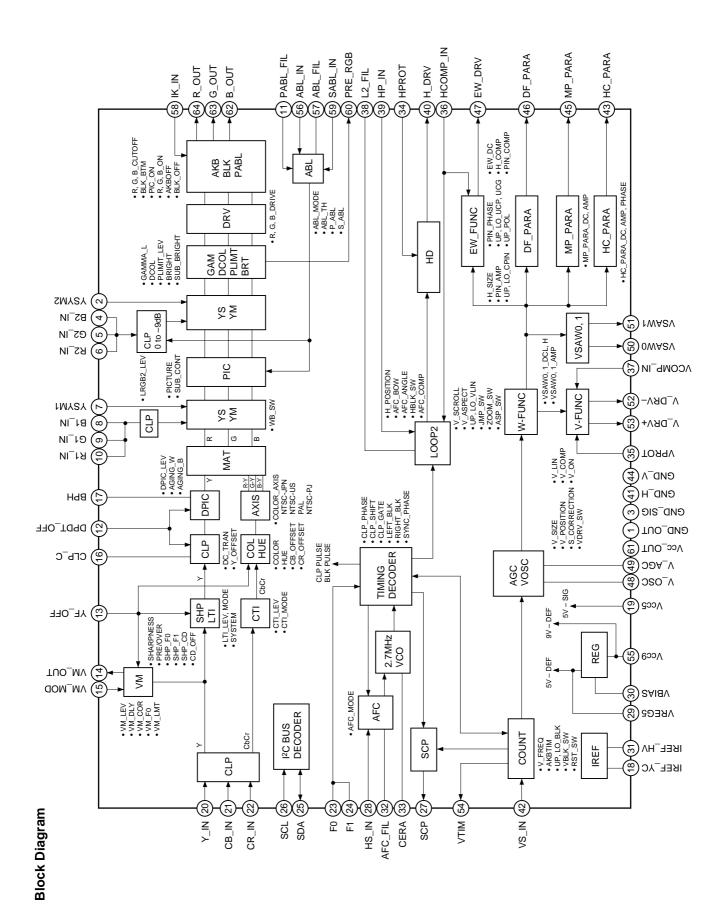

The CXA2150AQ is a bipolar IC which integrates base-band Y/C signal processing, RGB signal processing, horizontal sync signal processing that supports 15.7/31.5/33.75/37.9/45kHz, and a vertical deflection circuit that supports 50/60/100/120Hz into a single chip.

This IC has been developed for DTV, and realizes the configuration of a high-end TV system that supports 960i, 1080i, 720p, etc. in addition to 480i.

#### **Features**

- I<sup>2</sup>C bus supported

- YCbCr input offset adjustment circuit

- LTI and CTI circuits

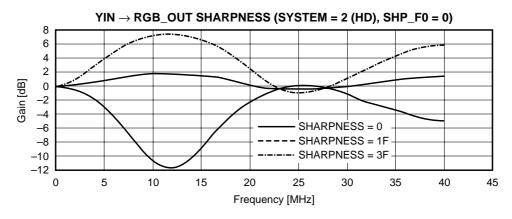

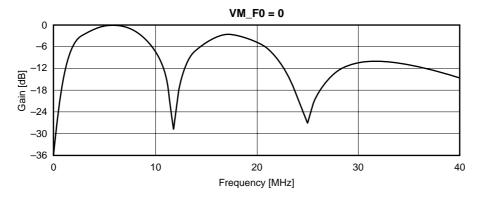

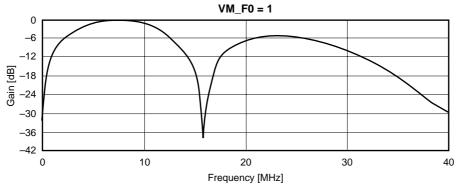

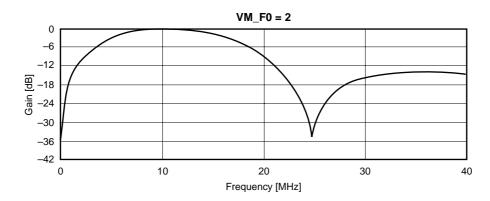

- Sharpness f0 switching circuit that supports band width of various input sources

- Color (Cr signal) dependent sharpness circuit

- Coring circuit for VM signal

- AKB system

- Various ABL functions

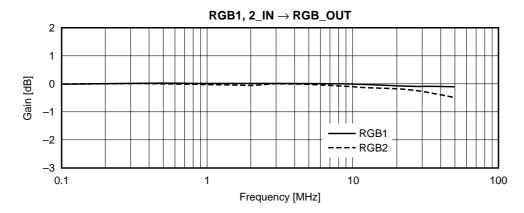

- Two sets of analog RGB inputs

- Horizontal sync processing that supports 15.7/31.5/33.75/37.9/45kHz

- Vertical deflection circuit that supports 50/60/100/120Hz

- Quick responsed VAGC when switching channels etc.

- Deflection compensation circuit capable of supporting various wide modes

- For flat-TV suitable various VSAW waveform and parabola output

#### **Applications**

Color TVs (4:3, 16:9)

#### **Structure**

Bipolar silicon monolithic IC

#### **Absolute Maximum Ratings** (Ta = 25°C)

| Supply voltage                                  | Vcc                                   | -0.3 to +10 | V  |

|-------------------------------------------------|---------------------------------------|-------------|----|

| <ul> <li>Operating temperature</li> </ul>       | Topr                                  | -20 to +75  | °C |

| <ul> <li>Storage temperature</li> </ul>         | Tstg                                  | -65 to +150 | °C |

| <ul> <li>Allowable power dissipation</li> </ul> | Po                                    | 1.7         | W  |

|                                                 | (when mounted on a 50mm × 50mm board) |             |    |

• Voltages at each pin —0.3 to Vcc9, Vcc\_OUT + 0.3 V

#### **Operating Conditions**

| Supply voltage | Vcc9, Vcc_OUT | $9.0 \pm 0.5$  | V |

|----------------|---------------|----------------|---|

|                | Vcc5          | $5.0 \pm 0.25$ | V |

Sony reserves the right to change products and specifications without prior notice. This information does not convey any license by any implication or otherwise under any patents or other right. Application circuits shown, if any, are typical examples illustrating the operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits.

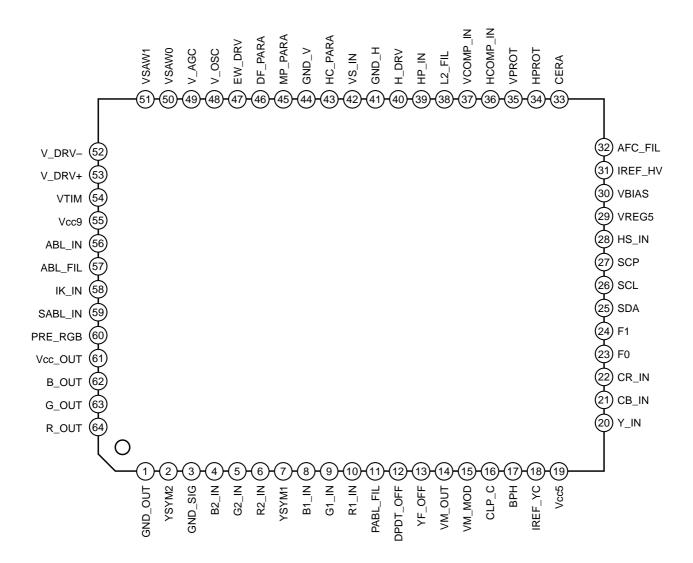

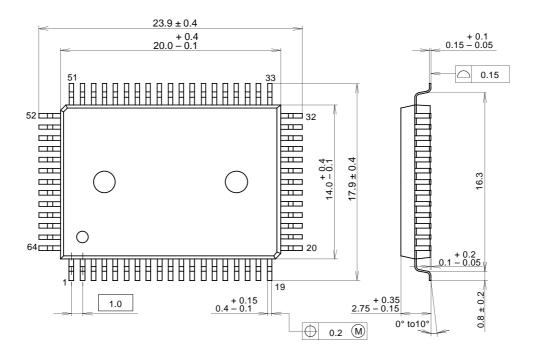

#### **Pin Configuration**

### **Pin Description**

|             | Fription                |                                                                 |                                                                                                                                                                                                                                |

|-------------|-------------------------|-----------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin<br>No.  | Symbol                  | Equivalent circuit                                              | Description                                                                                                                                                                                                                    |

| 1           | GND_OUT                 |                                                                 | GND for RGB_OUT output stage                                                                                                                                                                                                   |

|             |                         | Vcc_OUT Vcc5                                                    | YS2/YM2 control input. When the input level reaches the YM level, VM is OFF. <ys2sw> YS2: ON VIH ≥ 2.3V</ys2sw>                                                                                                                |

| 2           | YSYM2                   | 25μ 25μ<br>25μ 25μ<br>12.5k<br>77.5k                            | RGB2_IN selected YS2: OFF V <sub>IL</sub> ≤ 1.5V Internal RGB signal selected <ym2sw> YM2: ON V<sub>IH</sub> ≥ 0.9V Internal RGB signal set to -9.5dB YM2: OFF V<sub>IL</sub> ≤ 0.5V Internal RGB signal passed at 0dB</ym2sw> |

|             |                         |                                                                 | * Input voltage range: 0 to 5V                                                                                                                                                                                                 |

| 3           | GND_SIG                 |                                                                 | GND for Y/color difference and RGB systems.                                                                                                                                                                                    |

| 4<br>5<br>6 | B2_IN<br>G2_IN<br>R2_IN | Vcc_OUT                                                         | Analog R2, G2 and B2 signal inputs. Input a 0.7Vp-p, 100 IRE (no sync) signal via a capacitor. The pedestal is clamped to 3.2V. * Input voltage range: less than 5V                                                            |

| 7           | YSYM1                   | Vcc_OUT Vcc5  25µ  12.5k  7  7  7  7  7  7  7  7  7  7  7  7  7 | YS1/YM1 control input. When the input level reaches the YM level, VM is OFF. <ys1sw>     YS1: ON</ys1sw>                                                                                                                       |

| Pin<br>No.   | Symbol                  | Equivalent circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Description                                                                                                                                                                                                            |

|--------------|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 8<br>9<br>10 | B1_IN<br>G1_IN<br>R1_IN | Vcc_OUT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Analog R1, G1 and B1 signal inputs. Input a 0.7Vp-p, 100 IRE (no sync) signal via a capacitor. The pedestal is clamped to 3.75V.  * Input voltage range: less than 5V                                                  |

| 11           | PABL_FIL                | Vcc_OUT Vcc5  270  W 2k  W 25k  777  777  777  777                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Peak hold for peak ABL. A capacitor and resistor are connected between this pin and GND to form a LPF.                                                                                                                 |

| 12           | DPDT_OFF                | Vcc_OUT Vcc5  12.5  12.5  12.5  12.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7  17.7 | Muting of the dynamic picture operation (black expansion) and DC transmission ratio signal interval detection can be controlled by this pin.  MUTE: ON VIH ≥ 1V  MUTE: OFF VIL ≤ 0.4V  * Input voltage range: 0 to 5V  |

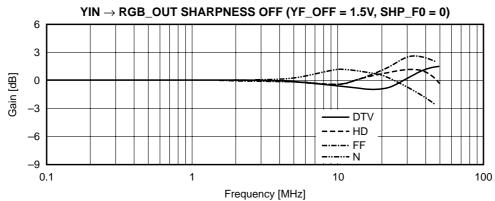

| 13           | YF_OFF                  | Vcc_OUT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | For turning off the VM, sharpness and color.  Ternary inputs are supported.  COLOR: OFF VIH ≥ 3V : ON VIL ≤ 2V  VM, SHP: OFF VIH ≥ 1.0V : ON VIL ≤ 0.4V  * Input voltage range: 0 to 5V                                |

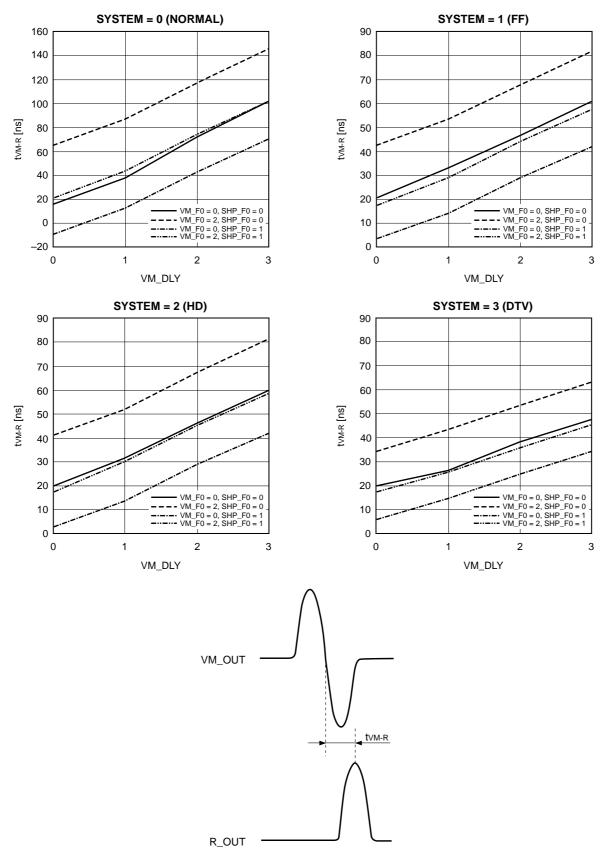

| 14           | VM_OUT                  | Vcc_OUT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | VM output. The differential waveforms of the Y signal are output with a positive polarity. The amplitude and phase of this waveform can be adjusted by the I <sup>2</sup> C bus.  * Allowable load current: -1 to +1mA |

| Pin<br>No. | Symbol  | Equivalent circuit         | Description                                                                                                                                                                                                                        |

|------------|---------|----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

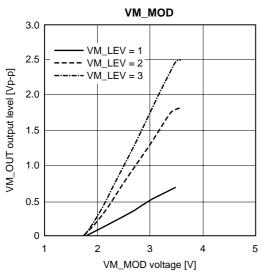

| 15         | VM_MOD  | Vcc_OUT                    | VM level modulation. Outputs are 0 at 1.5V or less, modulated from 1.5 to 3.5V, nonmodulated at 3.5V or more. At 1.5V or more output level can be adjusted by VM_LEV (I <sup>2</sup> C bus control) * Input voltage range: 0 to 5V |

| 16         | CLP_C   | Vcc_OUT                    | Connect a capacitor for Y system clamp. This capacitor also sets the DC transmission ratio.                                                                                                                                        |

| 17         | ВРН     | Vcc_OUT    1k 2k           | Connect a capacitor to GND for black detection of the dynamic picture (black stretch)                                                                                                                                              |

| 18         | IREF_YC | Vcc_OUT  150  \$50k  \$20k | Reference current setting for Y/color difference signal processing system. Connect to GND via the 4.7kΩ resistor (such as a metal film resistor) with an error of less than 1%.                                                    |

| 19         | Vcc5    |                            | Power supply for Y/color difference, RGB systems and I <sup>2</sup> C bus block.                                                                                                                                                   |

| Pin<br>No.     | Symbol                 | Equivalent circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Description                                                                                                                                                                                            |

|----------------|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

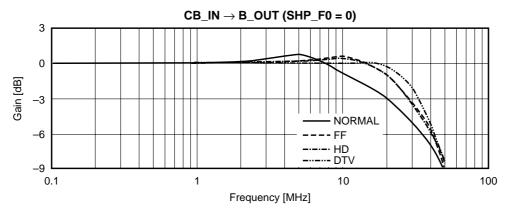

| 20<br>21<br>22 | Y_IN<br>CB_IN<br>CR_IN | Vcc_OUT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | External Y, Cb and Cr inputs Input 0.7Vp-p, 100 IRE Y, Cb and Cr signals (when Cb and Cr are at 100% color bar) via a capacitor. The pedestal is clamped to 3.5V.  * Input voltage range: less than 5V |

| 23<br>24       | F0<br>F1               | Vcc9 VREG5    75k   75k | Horizontal free-running frequency setting (See Table 1 on page 44.)                                                                                                                                    |

| 25             | SDA                    | 25 4k 2.5V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | I <sup>2</sup> C bus protocol SDA (Serial Data) input $V_{IH} \geq 3V \\ V_{IL} \leq 1.5V \\ V_{OL} \leq 0.6V$                                                                                         |

| 26             | SCL                    | 26 4k 777 2.5V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | I <sup>2</sup> C bus protocol SCL (Serial Clock) input $V_{IH} \geq 3V \\ V_{IL} \leq 1.5V$                                                                                                            |

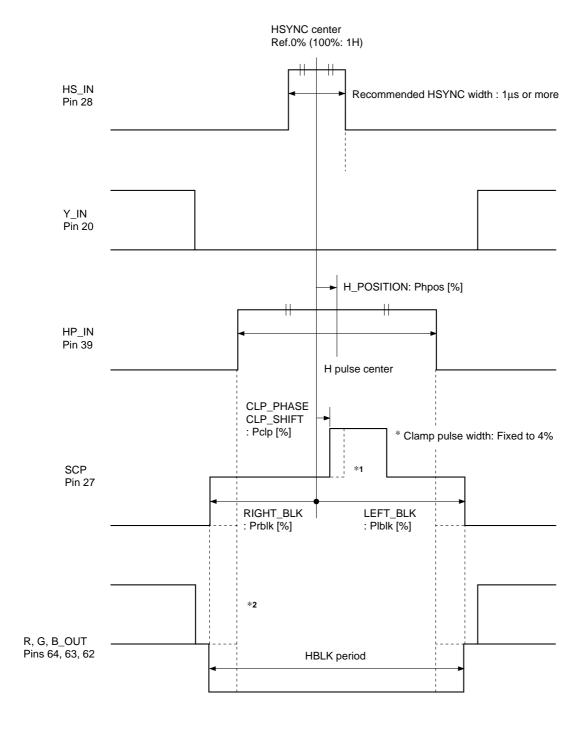

| 27             | SCP                    | Vcc9  150  1.2k  1.2k  11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Sand castle pulse output The approximately 0 to 5V CLP pulse is output superimposed on the approximately 0 to 2.5V HBLK and VBLK pulses.  * Allowable load current: -0.5 to +2mA                       |

| Pin<br>No. | Symbol         | Equivalent circuit                                         | Description                                                                                                                                                                        |

|------------|----------------|------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 28         | HS_IN          | Vcc9                                                       | HSYNC input Input at the sync phase.  Positive polarity input VIH ≥ 2.6V VIL ≤ 0.6V  * Input DC coupled                                                                            |

| 29<br>30   | VREG5<br>VBIAS | To Vcc for H system and the reference voltage for V system | Connect a NPN-Tr for the external feedback between Pin 30 (VBIAS) and Pin 29 (VREG5) to form 5V shunt regulator. Connect a capacitor of 100µF between Pin 29 (VREG5) and GND.      |

| 31         | IREF_HV        | 31                                                         | Reference current setting for H, V deflection systems. A $10k\Omega$ resistor with an error of less than 1% (such as a metal film resistor) is connected between this pin and GND. |

| 32         | AFC_FIL        | 32 1.2k 1.2k 1.2k 100k 1.2k 100k                           | AFC lag-lead filter<br>Connect the RC for the lag-lead filter.                                                                                                                     |

| Pin<br>No. | Symbol   | Equivalent circuit                               | Description                                                                                                                                                                                                                                                                                                                                |

|------------|----------|--------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 33         | CERA     | Vcc9                                             | Connect a 2.7MHz ceramic oscillator.                                                                                                                                                                                                                                                                                                       |

| 34         | HPROT    | Vcc9<br>69.5k<br>34 W 32.5k                      | HD output hold-down signal input When this pin is 2V or more for a 7V cycle or longer, the hold-down function operates so that the HD output is held to High Z.  In addition, the R, G and B outputs are completely blanked and "1" is output to the status register HNG.  To cancel this status, turn the IC power off and then on again. |

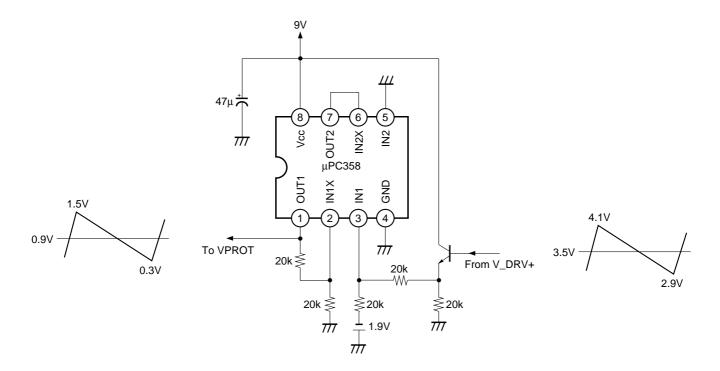

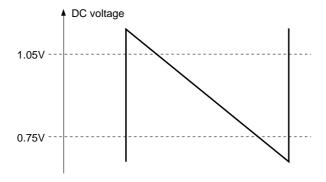

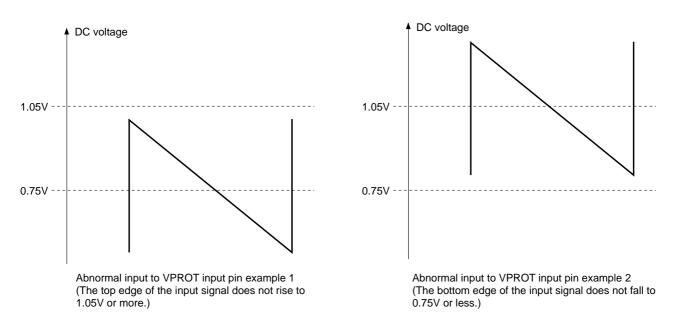

| 35         | VPROT    | Vcc9<br>2k<br>35<br>W                            | V protect input. When the protect function operates, the R, G and B outputs are completely blanked and "1" is output to the status register VNG. See Fig. 14 on page 59 for the input conditions.                                                                                                                                          |

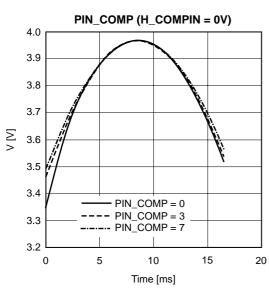

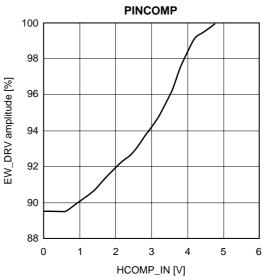

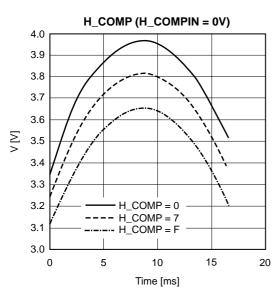

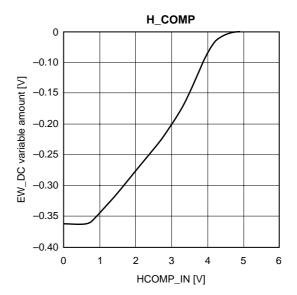

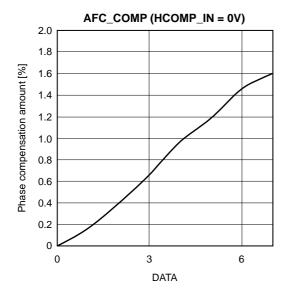

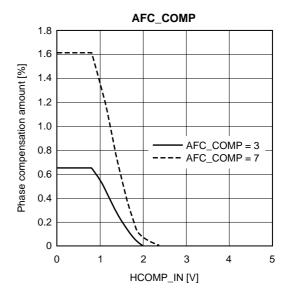

| 36         | HCOMP_IN | Vcc9  2k  36  W  38k  42.5k  10k  777  777       | Voltage input for high voltage fluctuation compensation High voltage compensation is performed for the EW_DRV signal DC amplitude and H_DRV signal phase. The control characteristics can be varied by H_COMP, PIN_COMP and AFC_COMP, respectively.  * Input voltage range: 0 to 5V                                                        |

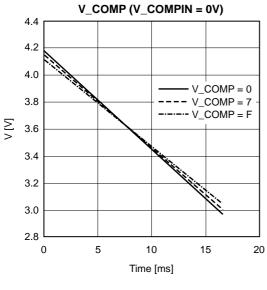

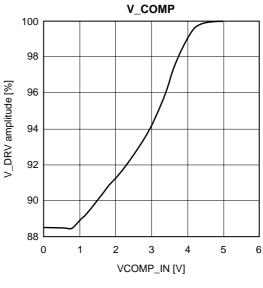

| 37         | VCOMP_IN | Vcc9<br>37<br>W → 1<br>38k ≨ 13.4k<br>9.7k ₹ 777 | Voltage input for high voltage fluctuation compensation High voltage compensation is performed for the V_DRV signal amplitude. The control characteristics can be varied by V_COMP.  * Input voltage range: 0 to 5V                                                                                                                        |

| Pin<br>No.     | Symbol                        | Equivalent circuit                                        | Description                                                                                                                                                                                                                                                                      |

|----------------|-------------------------------|-----------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 38             | L2_FIL                        | Vcc9<br>500 ≸<br>1.2k<br>W<br>25μ<br>777 777              | Filter for AFC 2nd loop Connect to GND via a capacitor. The AFC phase can also be controlled from this pin by leading current in and out of this capacitor. As the pin voltage rises, the picture shifts to the right. As the pin voltage falls, the picture shifts to the left. |

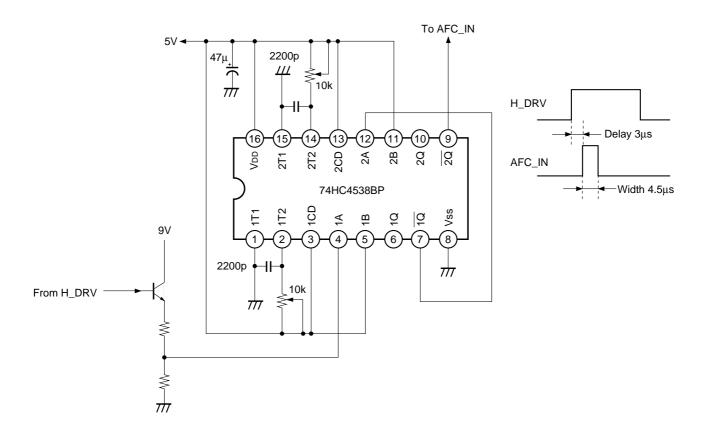

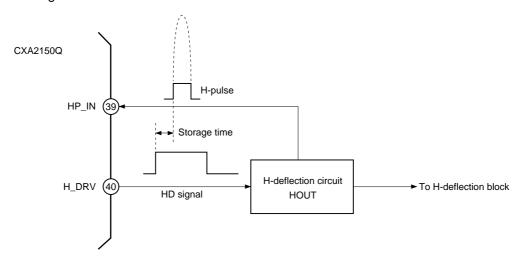

| 39             | HP_IN                         | 30k<br>30k<br>30k<br>30k<br>30k                           | H deflection pulse input for H AFC Input low level = 0V and high level = 5V pulse directly or a 5Vp-p pulse via an approximately 0.1µF capacitor.                                                                                                                                |

| 40             | H_DRV                         | Vcc9<br>150<br>W<br>150<br>W<br>150<br>1777 777 777       | H drive signal output This pin is output by an open collector. Set high level to 5V                                                                                                                                                                                              |

| 41             | GND_H                         |                                                           | GND for H deflection system.                                                                                                                                                                                                                                                     |

| 42             | VS_IN                         | Vcc9 VREG5  42 2k  50k  1.65V                             | VSYNC input Input at the sync phase.  Positive polarity input VIH ≥ 2.6V VIL ≤ 0.6V  * Input DC coupled                                                                                                                                                                          |

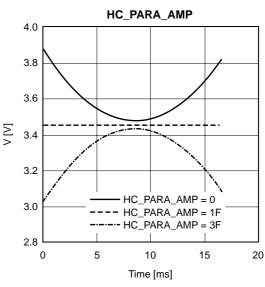

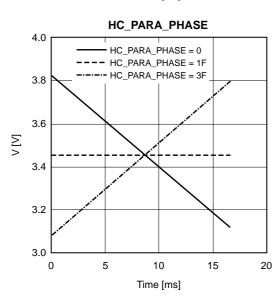

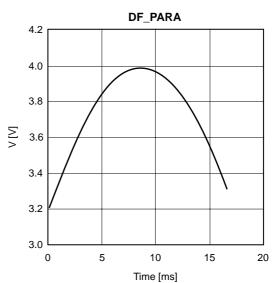

| 43<br>45<br>46 | HC_PARA<br>MP_PARA<br>DF_PARA | Vcc9<br>43<br>45<br>46<br>150<br>₹35k<br>46<br>777<br>777 | General-purpose V parabola wave output  * Allowable load current: –0.2 to +2.6mA                                                                                                                                                                                                 |

| Pin<br>No. | Symbol | Equivalent circuit                                                  | Description                                                                                                                                                      |

|------------|--------|---------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 44         | GND_V  |                                                                     | GND for V deflection system                                                                                                                                      |

| 47         | EW_DRV | Vcc9  150 51k  300μ 25μ  777 777                                    | V parabola wave output This is used to compensate the horizontal amplitude and the horizontal pin distortion.  * Allowable load current: -0.2 to +2.6mA          |

| 48         | V_OSC  | Vcc9                                                                | V sawtooth wave generation. Connect to GND via a 0.1μF capacitor. For the capacitor, use a PP (polypropylene) capacitor, or similar capacitor with a small tanδ. |

| 49         | V_AGC  | Vcc9                                                                | Sample-and-hold for AGC which maintains the V sawtooth wave at a constant amplitude Connect to GND via a 0.1µF capacitor.                                        |

| 50         | VSAW0  | Vcc9<br>150<br>150<br>177<br>177<br>177<br>177<br>177<br>177<br>177 | V sawtooth wave (VSAW0) output  * Allowable load current: -0.2 to +2.6mA                                                                                         |

| 51         | VSAW1  | Vcc9<br>150<br>\$17k<br>40k<br>1777<br>777<br>777<br>777            | V sawtooth wave (VSAW1) output  * Allowable load current: –0.2 to +2.6mA                                                                                         |

| Pin<br>No. | Symbol  | Equivalent circuit                                      | Description                                                                                                                                                                      |

|------------|---------|---------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 52         | V_DRV-  | Vcc9<br>150<br>55.1k<br>300μ                            | V sawtooth wave output (opposite polarity of V_DRV+)  * Allowable load current: -0.3 to +1.7mA                                                                                   |

| 53         | V_DRV+  | Vcc9<br>150<br>₹17k<br>55.1k<br>300μ                    | V sawtooth wave output (opposite polarity of V_DRV-)  * Allowable load current: -0.3 to +1.7mA                                                                                   |

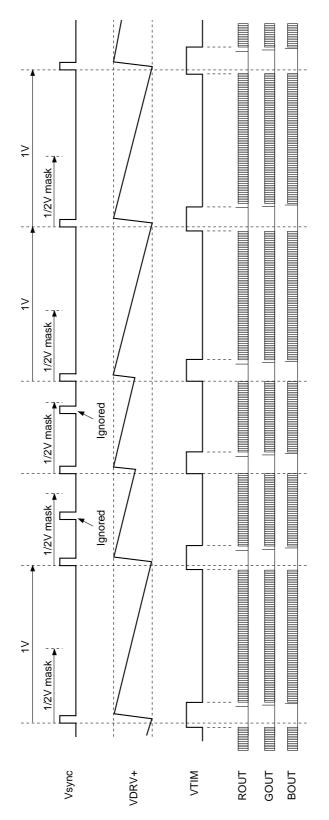

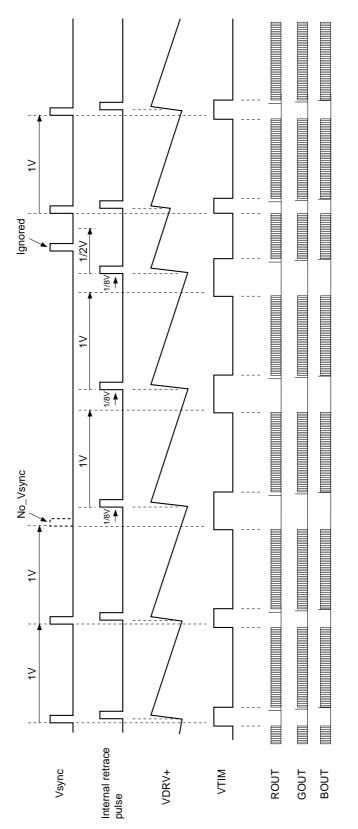

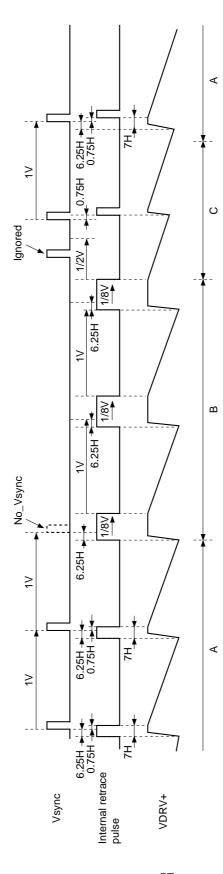

| 54         | VTIM    | Vcc9<br>150<br>150<br>150<br>150<br>177 777 777 777 777 | V timing pulse output Positive polarity pulses from 0 to 5V. This pin corresponds to VBLK position of RGB output during high period.                                             |

| 55         | Vcc9    |                                                         | Power supply for V deflection system.                                                                                                                                            |

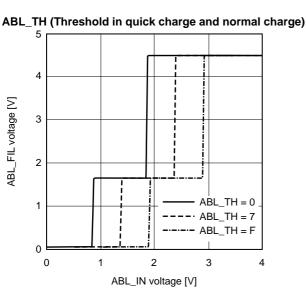

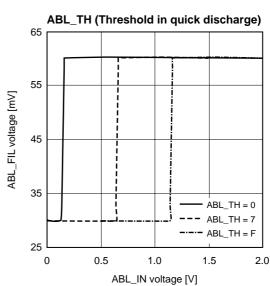

| 56         | ABL_IN  | Vcc_OUT Vcc5                                            | ABL control signal input This pin functions as the average value. The ABL_IN threshold voltage can be varied by the I <sup>2</sup> C bus ABL_TH.  * Input voltage range: 0 to 5V |

| 57         | ABL_FIL | Vcc_OUT Vcc5                                            | Connect a capacitor to form the LPF for the ABL_IN input signal.                                                                                                                 |

| Pin<br>No.     | Symbol                  | Equivalent circuit                            | Description                                                                                                                                                                                                                                   |

|----------------|-------------------------|-----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

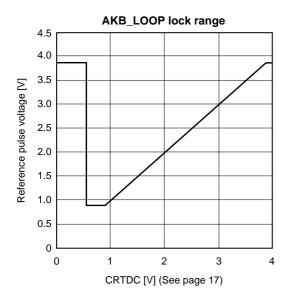

| 58             | IK_IN                   | 3.4V                                          | The reference pulses are returned to this pin. The CRT cathode current IK is converted to a voltage and input via a capacitor. This signal is clamped to 2.8V at the V retrace timing of the V blanking.  * Input voltage range: less than 5V |

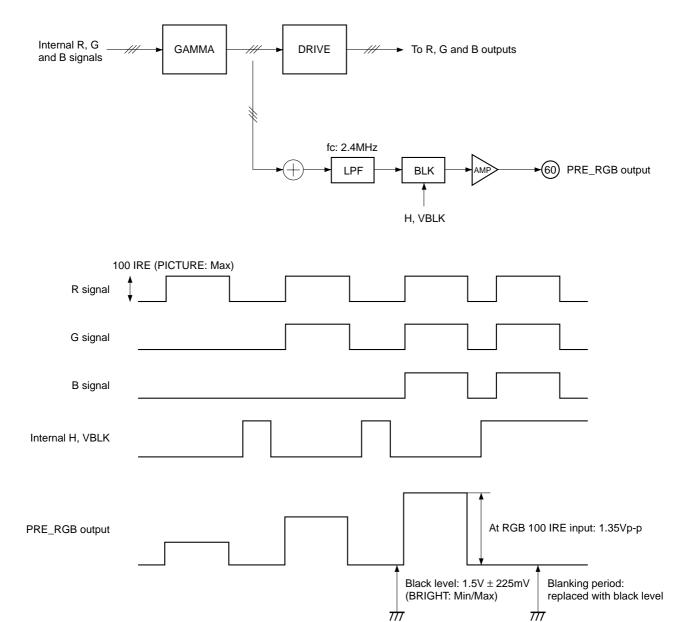

| 59             | SABL_IN                 | Vcc_OUT  200k  3.1V  9k  7/// 7// 7// 7// 7// | SABL compensation signal input PRE_RGB output signal (Pin 60) can be input via a external filter.  * Input voltage range: 0 to 5V                                                                                                             |

| 60             | PRE_RGB                 | Vcc_OUT    2k                                 | Mixed RGB signal output for high voltage fluctuation compensation and SABL compensation.  * Allowable load current: -0.8 to +0.4mA                                                                                                            |

| 61             | Vcc_OUT                 |                                               | Power supply for RGB system output stage.                                                                                                                                                                                                     |

| 62<br>63<br>64 | B_OUT<br>G_OUT<br>R_OUT | Vcc_OUT  1k  1k  5k 63 64  \$500              | R, G and B signal outputs. A 2.6Vp-p signal is output at 100 IRE.  * Allowable load current: –3.7 to +5mA                                                                                                                                     |

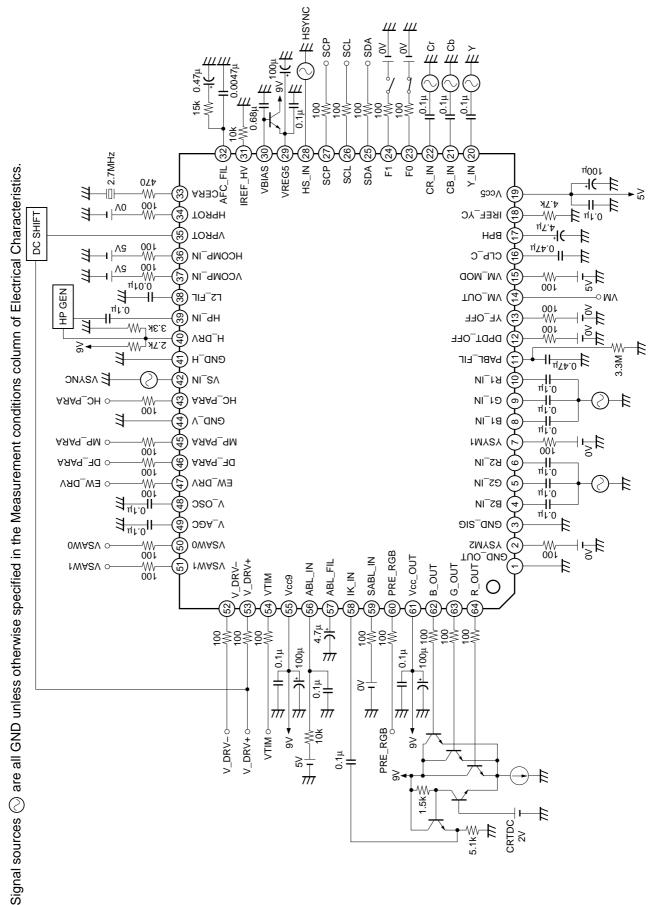

Electrical Characteristics Measurement conditions: Ta = 25°C, Vcc9 = Vcc\_OUT = 9V, Vcc5 = 5V, GND\_OUT = GND\_SIG = GND\_H = GND\_V = 0V Measures the following after setting the I<sup>2</sup>C bus register as shown in "I<sup>2</sup>C bus Register Initial Settings".

| No.              |                                        |        |                                                                                                                             |                      |                                                                                                                                 |      |                |      |      |

|------------------|----------------------------------------|--------|-----------------------------------------------------------------------------------------------------------------------------|----------------------|---------------------------------------------------------------------------------------------------------------------------------|------|----------------|------|------|

|                  | Item                                   | Symbol | Measurement conditions                                                                                                      | Measure-<br>ment pin | Measurement contents                                                                                                            | Min. | Тур.           | Мах. | Unit |

| 1 5              | 5V system current consumption          | ICC5   |                                                                                                                             | 19                   | Measure the pin inflow current.                                                                                                 | 55   | 80             | 115  | mA   |

| 2 9              | 9V system current consumption          | 6001   |                                                                                                                             | 55, 61               | Measure the pin inflow current.                                                                                                 | 18   | 33             | 52   | mA   |

| 3 50             | 5V regulator current consumption       | ICCreg |                                                                                                                             | *29                  | * Measure the collector current of the external NPN-Tr.                                                                         | 17   | 27             | 38   | mA   |

| 4 5              | 5V regulator voltage                   | VREG   |                                                                                                                             | 29                   | Measure the pin voltage.                                                                                                        | 4.8  | 2              | 5.2  | >    |

| Deflec           | Deflection system items                |        |                                                                                                                             |                      |                                                                                                                                 |      |                |      |      |

| 5 fre            | Horizontal free-running<br>frequency 1 | fHFR1  | AFC_MODE = 0,<br>F0: 0V, F1: 0V                                                                                             |                      |                                                                                                                                 | 15.4 | 15.74          | 16.1 | kHz  |

| 6<br>fre         | Horizontal free-running<br>frequency 2 | fHFR2  | AFC_MODE = 0,<br>F0: Open, F1: 0V                                                                                           |                      |                                                                                                                                 | 31.1 | 31.5           | 31.9 | kHz  |

| 7 Hr             | Horizontal free-running<br>frequency 3 | fHFR3  | AFC_MODE = 0,<br>F0: 0V, F1: Open                                                                                           |                      | Measure the output frequency.                                                                                                   | 33.4 | 33.83          | 34.2 | kHz  |

| 8                | Horizontal free-running<br>frequency 4 | fHFR4  | AFC_MODE = 0,<br>F0: Open, F1: 5V                                                                                           | 40                   |                                                                                                                                 | 37.2 | 37.6           | 38.0 | kHz  |

| 9<br>1<br>1<br>1 | Horizontal free-running<br>frequency 5 | fHFR5  | AFC_MODE = 0,<br>F0: Open, F1: Open                                                                                         |                      |                                                                                                                                 | 44.7 | 45.1           | 45.5 | kHz  |

| 10 H             | Horizontal sync pull-in<br>range       | ΔfHR   | Input HSYNC                                                                                                                 |                      | Normalize the pull-in range when the HSYNC input frequency is shifted from the free-running frequency. (Confirm the HLOCK = 1.) | I    | <del>1</del> 3 | l    | %    |

| <u>+</u>         | H_DRV output pulse duty                | Hdduty |                                                                                                                             |                      | Measure the pulse duty of H_DRV output.                                                                                         | 43.4 | 43.74          | 44   | %    |

| 12 Si            | SCP CLP output pulse width             | tCLPW  | Measure the pulse width for the section where the SCP CLP output is high level, and normalize it with the horizontal cycle. |                      | tCLPW T                                                                                                                         | 3.2  | 3.7            | 4.2  | %    |

| 13 S             | SCP CLP output high level              | VSCPH  | Measure the SCP CLP output high level.                                                                                      | 27                   |                                                                                                                                 | 4.7  | 2              | -    | >    |

| 14 S             | SCP BLK output high level              | VSCPM  | Measure the SCP BLK output high level.                                                                                      |                      | 777 777 777 777 777 VSCPM VSCPH VSCPH                                                                                           | 2.35 | 2.5            | 2.65 | >    |

| 15<br>S          | SCP output low level                   | VSCPL  | Measure the SCP output low level.                                                                                           |                      |                                                                                                                                 | 0.05 | 0.2            | 9.0  | >    |

| Š. | ltem                              | Symbol | Measurement conditions | Measure-<br>ment pin | Measurement contents           | Min. | Typ. | Мах. | Unit |

|----|-----------------------------------|--------|------------------------|----------------------|--------------------------------|------|------|------|------|

| 16 | V_DRV<br>output amplitude         | VDp-p  |                        | 50 53                | Measure the V_DRV output Vp-p  | 1.07 | 1.2  | 1.3  | >    |

| 17 | V_DRV<br>output center potential  | VDdc   |                        | 02, 20               | V_DRV+                         | 3.39 | 3.5  | 3.63 | >    |

| 18 | EW_DRV<br>output amplitude        | VEWp-p | Input VSYNC.           | 27                   | Measure the EW_DRV output Vp-p | 0.39 | 0.54 | 0.65 | >    |

| 19 | EW_DRV<br>output center potential | VEWdc  |                        | ì                    | VSYNC                          | 3.78 | 4    | 4.16 | >    |

| 20 | VTIM<br>output high level         | VTIMH  |                        | 7                    | -                              | 4.65 | 5    | 5.05 | >    |

| 21 | VTIM<br>output low level          | VTIML  |                        | 5                    | 777 777<br>VTIMH VTIML         | 0.15 | 0.25 | 0.35 | >    |

| ş<br>Ş | Item                  | Symbol | Measurement conditions                                                      | Measure- | Measurement contents                                                                                 | Min. | Typ. | Мах. | Unit   |

|--------|-----------------------|--------|-----------------------------------------------------------------------------|----------|------------------------------------------------------------------------------------------------------|------|------|------|--------|

| Sig    | Signal system items   |        |                                                                             |          |                                                                                                      |      |      |      |        |

| 22     | RGB output            | VRGB   | 100 IRE signal input to Y_IN (Pin 20)                                       | 62. 63.  | Measure the output level.                                                                            | 2.18 | 2.56 | 2.84 | >      |

| 23     | RGB linearity         | VLIN   | 50 100<br>Staircase wave input to Y_IN (Pin 20)                             | 64       | $\sqrt{\frac{1}{\sqrt{2}}} \sqrt{\frac{1}{\sqrt{11}}} \sqrt{\frac{1}{\sqrt{2} \times 2}} \times 100$ | 96   | 100  | 104  | %      |

| 24     | RGB1 gain             | GL1    | 100 IRE signal input to $G1_{IN}$ (Pin 9), YSYM1 (Pin 7) = $5V$             | 63       | Compare the output level to VRGB                                                                     | -0.8 | -0.2 | 0.3  | dВ     |

| 25     | RGB2 gain             | GL2    | 100 IRE signal input to G2_IN (Pin 5), YSYM2 (Pin 2) = 5V                   | 3        | Compare the output level to VRGB                                                                     | -0.8 | -0.1 | 0.8  | dВ     |

| 26     | VM output             | W//    | 50 IRE/8MHz                                                                 | 41       | Measure the VM_OUT level.                                                                            | 1.75 | 2.56 | 3.15 | >      |

| 27     | HUE center            | θв     | Y_IN (Pin 20)  CB_IN (Pin 21)  CR_IN (Pin 22)  CB = 572mVp-p  Cr = 406mVp-p | 62       | θB = tan <sup>-1</sup> VB level with Cr input                                                        | 8    | 7.4- | 7    | бәр    |

| 28     | BRIGHT center Rch     | VBRT-R |                                                                             | 64       | [                                                                                                    | -420 | -250 | -45  | Λm     |

| 29     | BRIGHT center Gch     | VBRT-G |                                                                             | 63       |                                                                                                      | -420 | -250 | -45  | νm     |

| 30     | BRIGHT center Bch     | VBRT-B |                                                                             | 62       | 777 777 VREFP VBLK VPED                                                                              | -420 | -250 | -45  | /m     |

| 31     | RGB output VBLK level | VBLK-R |                                                                             | 64       |                                                                                                      | 200  | 400  | 550  | m<br>> |

Electrical Characteristics Measurement Circuit

# **Electrical Characteristics Measurement Input Signals**

#### **DC SHIFT**

#### HP GEN.

# Electrical Characteristics Measurement Conditions "I<sup>2</sup>C bus Register Initial Settings"

| Register name | No. of bits | Setting | Description                |

|---------------|-------------|---------|----------------------------|

| PIC_ON        | 1           | 1       | R, G, B outputs on         |

| R_ON          | 1           | 1       | R output on                |

| G_ON          | 1           | 1       | G output on                |

| B_ON          | 1           | 1       | B output on                |

| DCOL          | 2           | 0       | DCOL off                   |

| WB_SW         | 1           | 0       | OFF                        |

| GAMMA_L       | 1           | 0       | GAMMA fine adjustment off  |

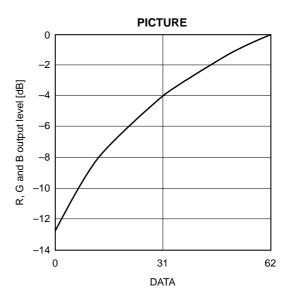

| PICTURE       | 6           | 3Fh     | Max.                       |

| BLK_BTM       | 2           | 0       | Min.                       |

| HUE           | 6           | 1Fh     | Center                     |

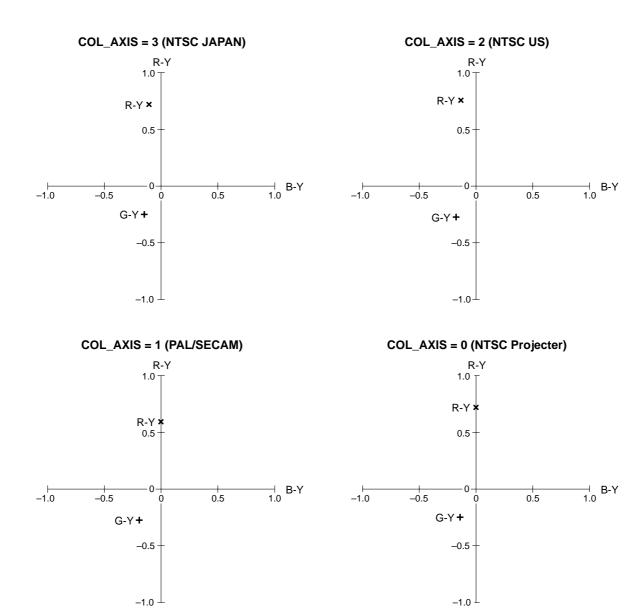

| COL_AXIS      | 2           | 3       | NTSC Japan                 |

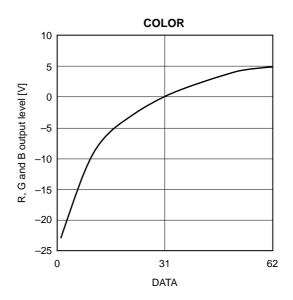

| COLOR         | 6           | 1Fh     | Center                     |

| CTI_LEV       | 2           | 0       | CTI off                    |

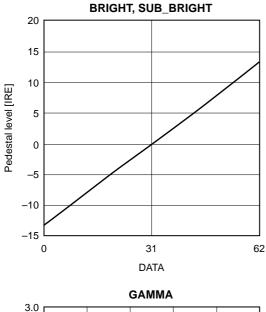

| BRIGHT        | 6           | 1Fh     | Center                     |

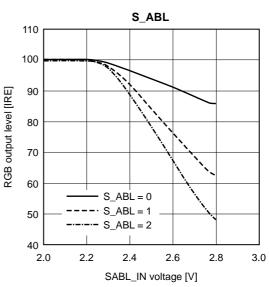

| S_ABL         | 2           | 0       | SABL off                   |

| SHARPNESS     | 6           | 1Fh     | Center                     |

| LTI_LEV       | 2           | 0       | LTI off                    |

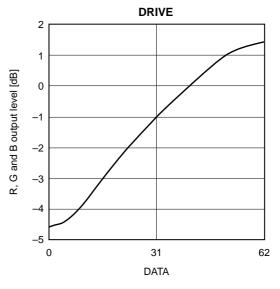

| R_DRIVE       | 6           | 29h     | 0dB                        |

| PLIMIT_LEV    | 2           | 3       | Max.                       |

| G_DRIVE       | 6           | 29h     | 0dB                        |

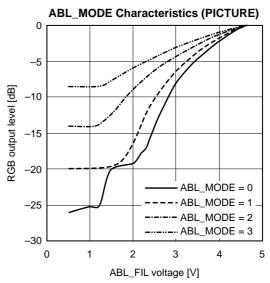

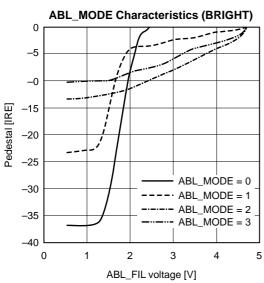

| ABL_MODE      | 2           | 0       | Picture/Only               |

| B_DRIVE       | 6           | 29h     | 0dB                        |

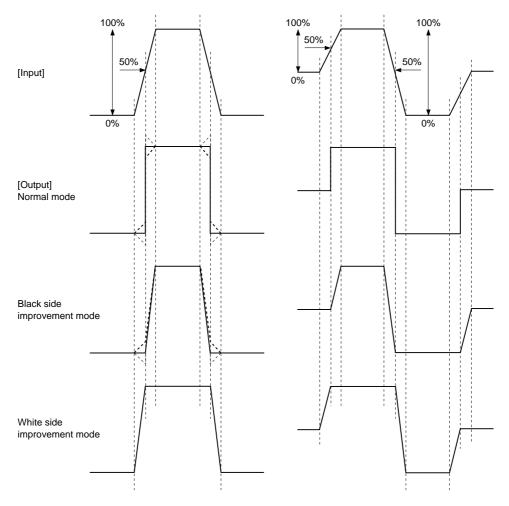

| CTI_MODE      | 2           | 0       | B/W both sides improvement |

| SUB_BRIGHT    | 6           | 1Fh     | Center                     |

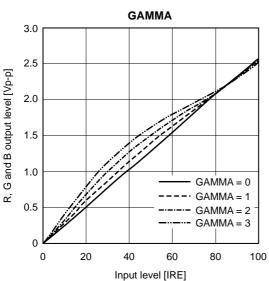

| GAMMA         | 2           | 0       | GAMMA off                  |

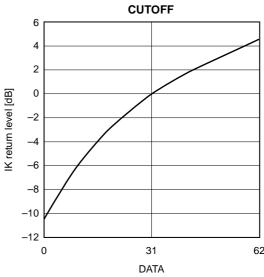

| R_CUTOFF      | 6           | 1Fh     | Center                     |

| LTI_MODE      | 2           | 0       | B/W both sides improvement |

| G_CUTOFF      | 6           | 1Fh     | Center                     |

| DPIC_LEV      | 2           | 0       | OFF                        |

| B_CUTOFF      | 6           | 1Fh     | Center                     |

| DC_TRAN       | 2           | 0       | DC transmission ratio 100% |

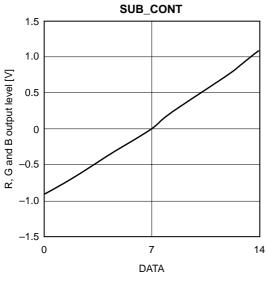

| SUB_CONT      | 4           | 7h      | Center                     |

| LRGB2_LEV     | 4           | Fh      | 0dB                        |

| P_ABL         | 4           | Fh      | Max.                       |

| ABL_TH        | 4           | 0       | Min.                       |

| Register name | No. of bits | Setting | Description                   |

|---------------|-------------|---------|-------------------------------|

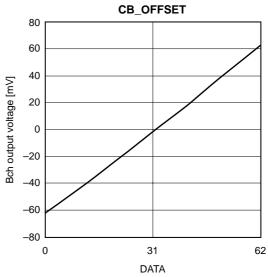

| CB_OFFSET     | 6           | 1Fh     | Center                        |

| AGING_W       | 1           | 0       | OFF                           |

| AGING_B       | 1           | 0       | OFF                           |

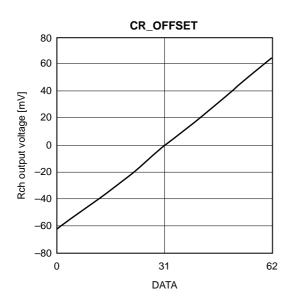

| CR_OFFSET     | 6           | 1Fh     | Center                        |

| SYSTEM        | 2           | 2       | HD mode                       |

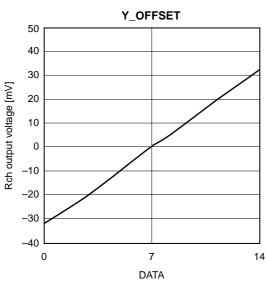

| Y_OFFSET      | 4           | 7h      | Center                        |

| VM_LEV        | 2           | 3       | Max.                          |

| SHP_F0        | 1           | 1       | 16MHz                         |

| CD_OFF        | 1           | 1       | SHP_CD function off           |

| SHP_CD        | 2           | 0       | OFF                           |

| SHP_F1        | 2           | 0       | OFF                           |

| PRE/OVER      | 2           | 1       | 1:1                           |

| VM_COR        | 2           | 0       | OFF                           |

| VM_F0         | 2           | 0       | Min.                          |

| VM_LMT        | 2           | 3       | Maximum limit                 |

| VM_DLY        | 2           | 0       | VM output delay Max.          |

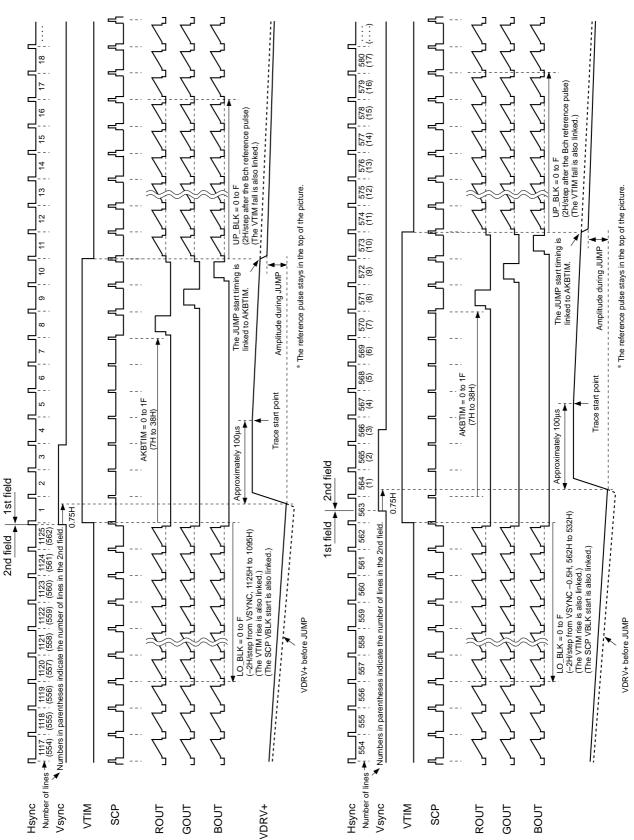

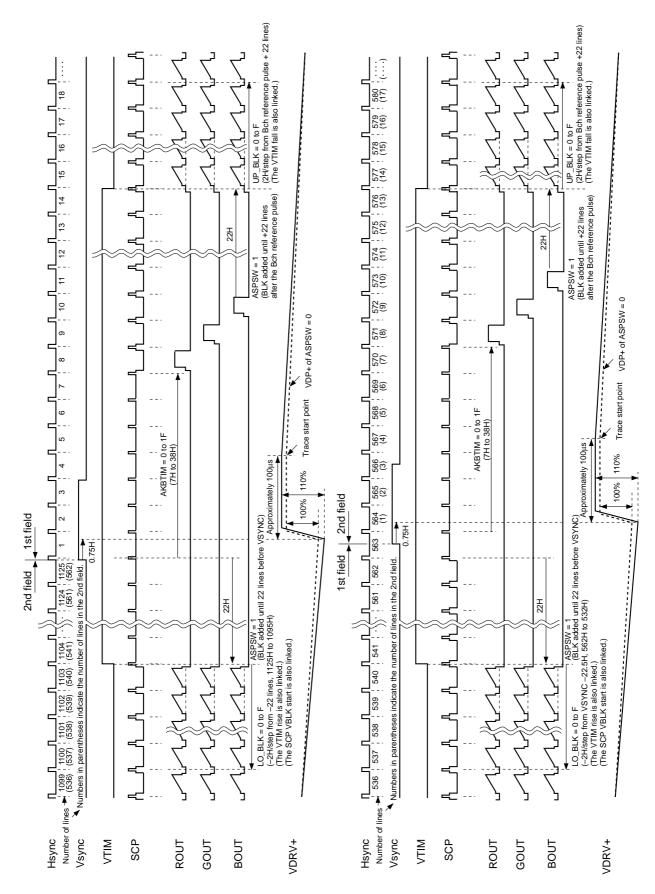

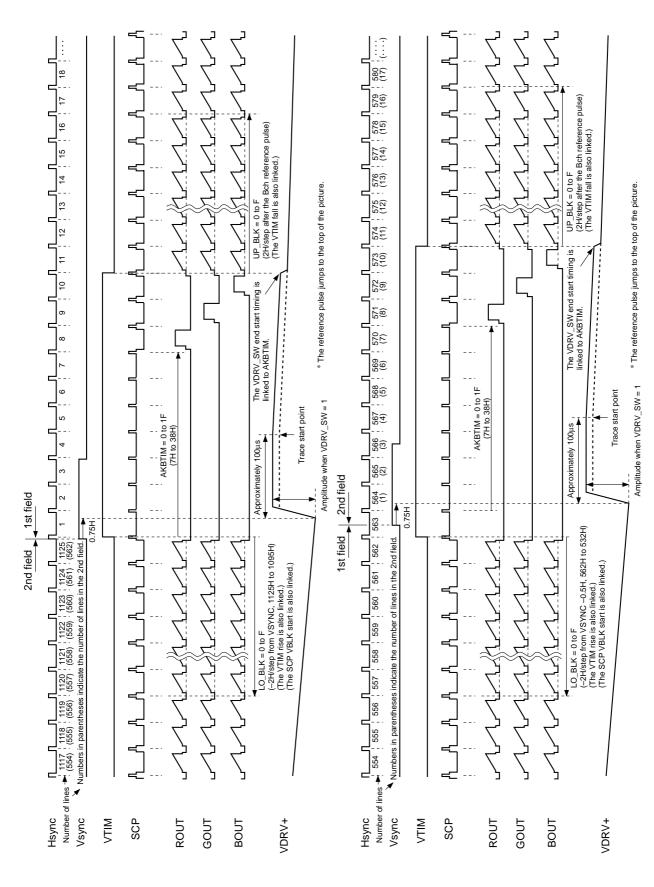

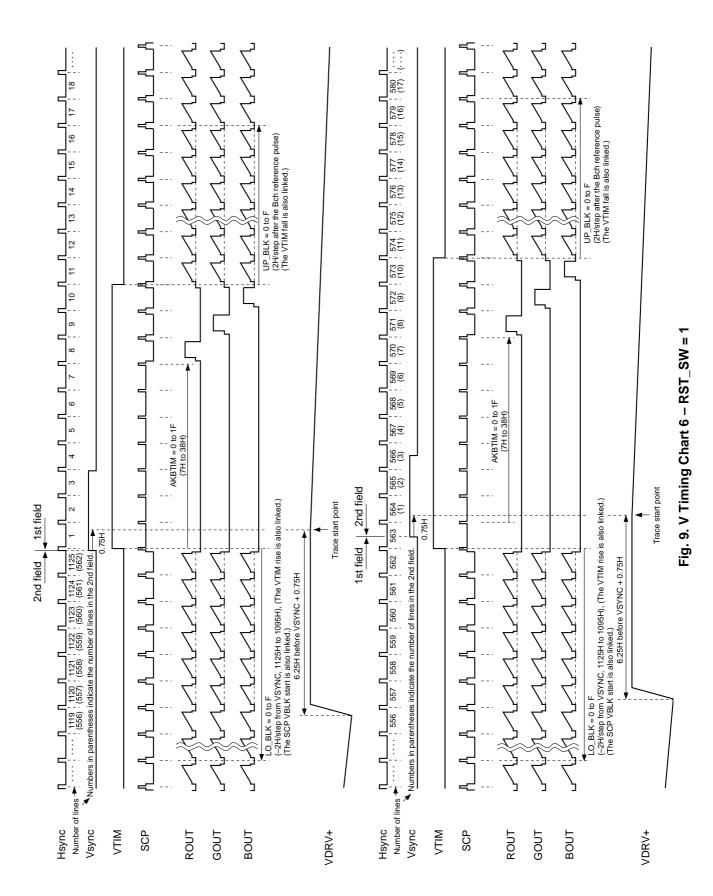

| AKB_TIM       | 5           | 0h      | Bch REF-P 10H                 |

| BLK_OFF       | 1           | 0       | Blanking on                   |

| AKBOFF        | 1           | 0       | AKB mode                      |

| UP_BLK        | 4           | 0h      | VBLK-end 0H after Bch REF-P   |

| LO_BLK        | 4           | 0h      | VBLK-start 0H before VSYNC    |

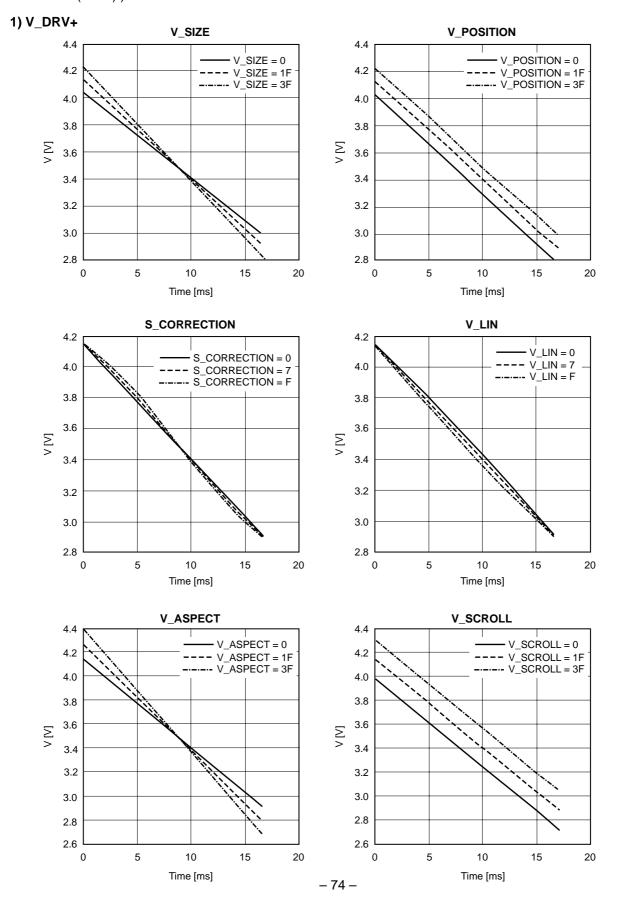

| V_SIZE        | 6           | 1Fh     | Center                        |

| V_ON          | 1           | 1       | V_DRV output on               |

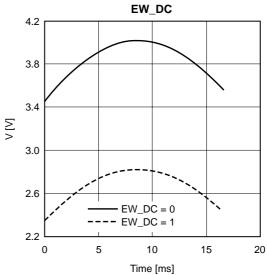

| EW_DC         | 1           | 0       | OFF                           |

| V_POSITION    | 6           | 1Fh     | Center                        |

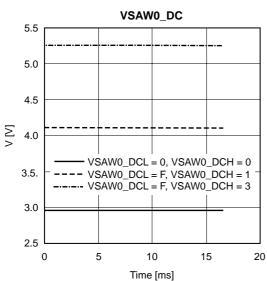

| VSAW0_DCH     | 2           | 1       | Center                        |

| V_LIN         | 4           | 7h      | Center                        |

| S_CORRECTION  | 4           | 0h      | Min.                          |

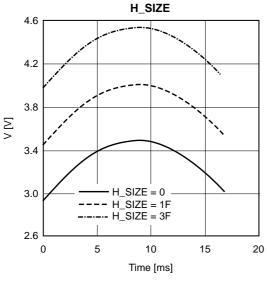

| H_SIZE        | 6           | 1Fh     | Center                        |

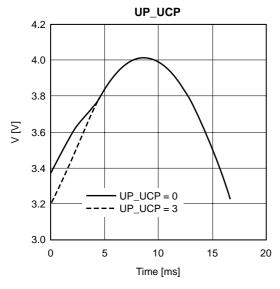

| UP_UCP        | 2           | 0       | Most inside point compensated |

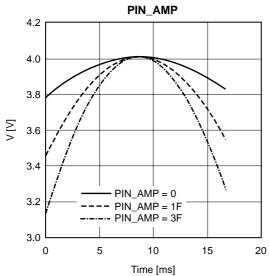

| PIN_AMP       | 6           | 1Fh     | Center                        |

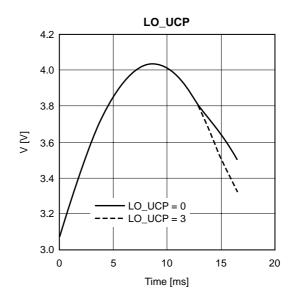

| LO_UCP        | 2           | 0       | Most inside point compensated |

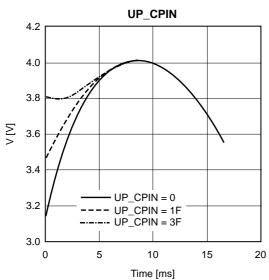

| UP_CPIN       | 6           | 1Fh     | Center                        |

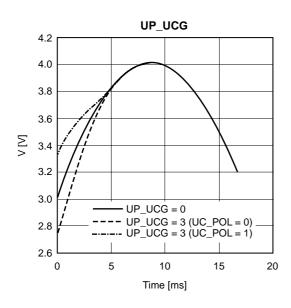

| UP_UCG        | 2           | 0       | Min.                          |

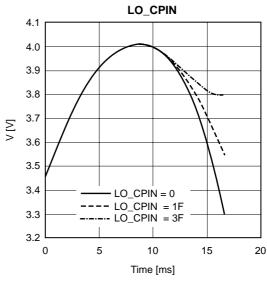

| LO_CPIN       | 6           | 1Fh     | Center                        |

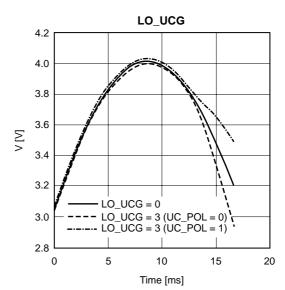

| LO_UCG        | 2           | 0       | Min.                          |

| Register name | No. of bits | Setting | Description                       |

|---------------|-------------|---------|-----------------------------------|

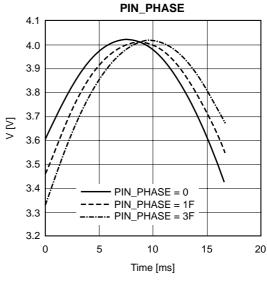

| PIN_PHASE     | 6           | 1Fh     | Center                            |

| UC_POL        | 1           | 0       | H-size small on compensated parts |

| VBLK_SW       | 1           | 1       | UP/LO_BLK only                    |

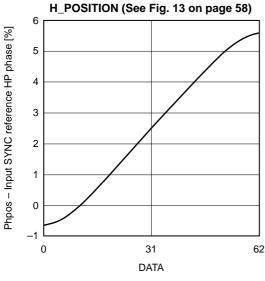

| H_POSITION    | 6           | 1Fh     | Center                            |

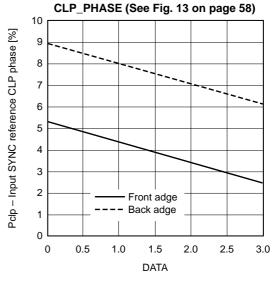

| CLP_SHIFT     | 1           | 0       | CLP_PHASE settings                |

| SYNC_PHASE    | 2           | 0       | HSYNC delay 0%                    |

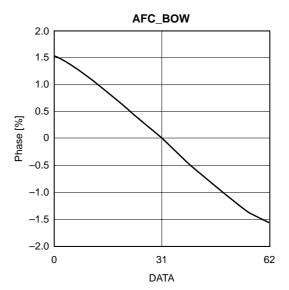

| AFC_BOW       | 6           | 1Fh     | Center                            |

| AFC_MODE      | 2           | 2       | Medium gain                       |

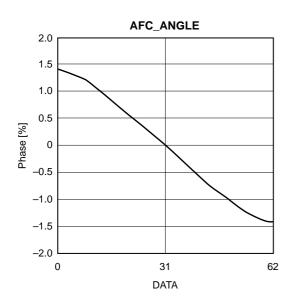

| AFC_ANGLE     | 6           | 1Fh     | Center                            |

| RST_SW        | 1           | 0       | Retrace after VSYNC               |

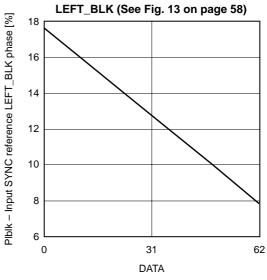

| LEFT_BLK      | 6           | 1Fh     | Center                            |

| CLP_PHASE     | 2           | 3       | Min.                              |

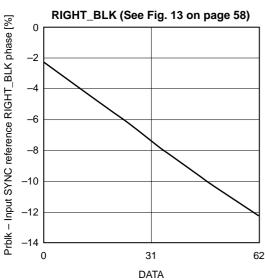

| RIGHT_BLK     | 6           | 1Fh     | Center                            |

| CLP_GATE      | 1           | 0       | Gating function off               |

| HBLK_SW       | 1           | 1       | HBLK control enable               |

| V_ASPECT      | 6           | 0h      | Min.                              |

| ZOOM_SW       | 1           | 0       | ZOOM_SW off                       |

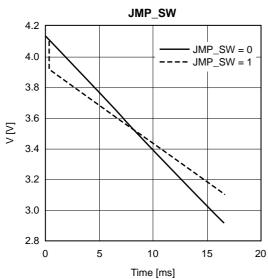

| JMP_SW        | 1           | 0       | JMP_SW off                        |

| V_SCROLL      | 6           | 1Fh     | Center                            |

| VFREQ         | 2           | 1       | 60Hz mode                         |

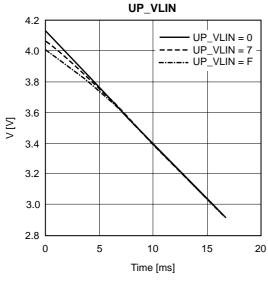

| UP_VLIN       | 4           | 0h      | Min.                              |

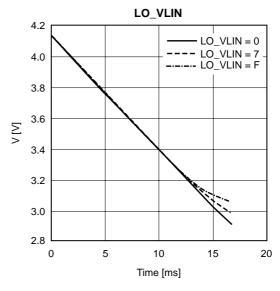

| LO_VLIN       | 4           | 0h      | Min.                              |

| V_COMP        | 4           | 0h      | Compensation off                  |

| H_COMP        | 4           | 0h      | Compensation off                  |

| VSAW0_DCL     | 4           | Fh      | Center                            |

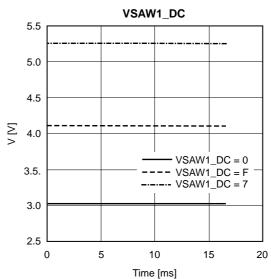

| VSAW1_DC      | 4           | 7h      | Center                            |

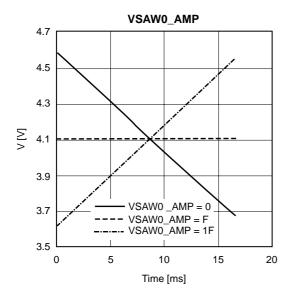

| VSAW0_AMP     | 5           | Fh      | Amplitude off                     |

| PIN_COMP      | 3           | 0       | Compensation off                  |

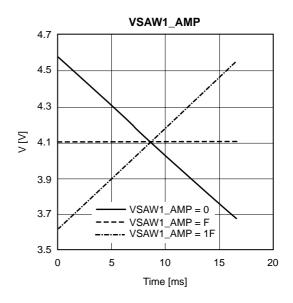

| VSAW1_AMP     | 5           | Fh      | Amplitude off                     |

| AFC_COMP      | 3           | 0       | Compensation off                  |

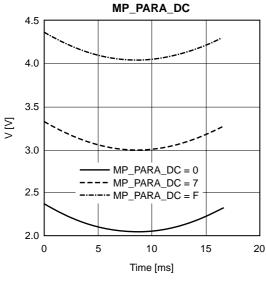

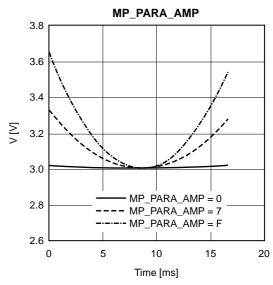

| MP_PARA_DC    | 4           | 7h      | Center                            |

| MP_PARA_AMP   | 4           | 0h      | Amplitude off                     |

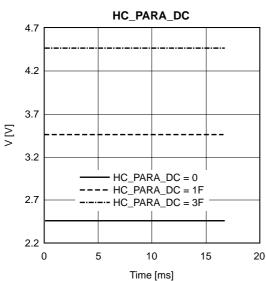

| HC_PARA_DC    | 6           | 1Fh     | Center                            |

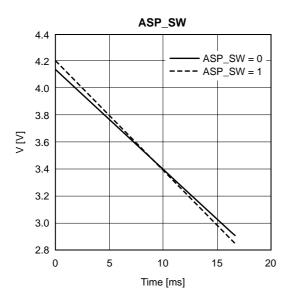

| ASP_SW        | 1           | 0       | OFF                               |

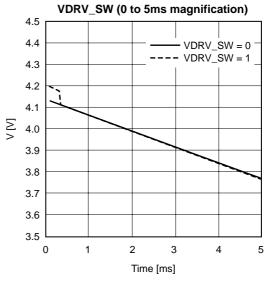

| VDRV_SW       | 1           | 0       | OFF                               |

| HC_PARA_AMP   | 6           | 1Fh     | Amplitude off                     |

| HC_PARA_PHASE | 6           | 1Fh     | Center                            |

Definition of I<sup>2</sup>C bus Registers Slave address 86H: Slave Receiver 8 Control Register (Register Tables \*: Undefined) 87H: Slave Transmitter

| Control Register (Re | glotor rabico | ·. Ondominoc        | 4)                |         |       |              |           |            |

|----------------------|---------------|---------------------|-------------------|---------|-------|--------------|-----------|------------|

| Sub Address          | Bit 7         | Bit 6               | Bit 5             | Bit 4   | Bit 3 | Bit 2        | Bit 1     | Bit 0      |

| XXX00000 00h         | PIC_ON        | R_ON                | G_ON              | B_ON    | DC    | OL           | WB_SW     | GAMMA_L    |

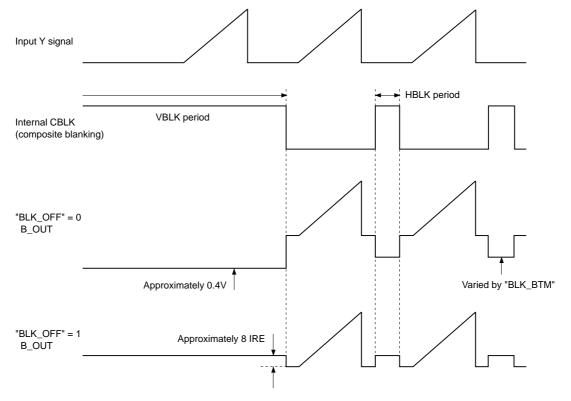

| XXX00001 01h         |               |                     | PICT              | URE     |       |              | BLK_      | _BTM       |

| XXX00010 02h         |               |                     | H                 | JE      |       |              | COL       | _AXIS      |

| XXX00011 03h         |               |                     | COI               | LOR     |       |              | CTI_      | _LEV       |

| XXX00100 04h         |               |                     | BRI               | GHT     |       |              | S_/       | ABL        |

| XXX00101 05h         |               |                     | SHARI             | PNESS   |       |              | LTI_      | LEV        |

| XXX00110 06h         |               |                     | R_D               | RIVE    |       |              |           | T_LEV      |

| XXX00111 07h         |               |                     | G_D               | RIVE    |       |              | ABL_I     | MODE       |

| XXX01000 08h         |               |                     |                   | RIVE    |       |              |           | MODE       |

| XXX01001 09h         |               |                     |                   | BRIGHT  |       |              |           | ИМА        |

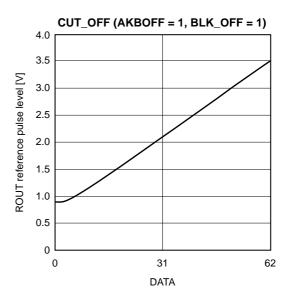

| XXX01010 0Ah         |               |                     |                   | ITOFF   |       |              |           | MODE       |

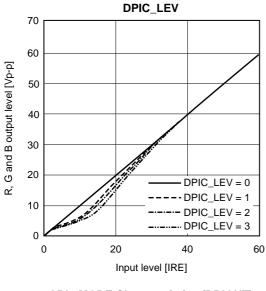

| XXX01011 0Bh         |               |                     |                   | JTOFF   |       |              | DPIC      | _LEV       |

| XXX01100 0Ch         |               |                     |                   | ITOFF   |       |              | I .       | TRAN       |

| XXX01101 0Dh         |               | SUB_0               |                   |         |       |              | 2_LEV     |            |

| XXX01110 0Eh         |               | P_ <i>P</i>         |                   |         |       | ABL          | _TH       |            |

| XXX01111 0Fh         |               |                     |                   | FFSET   |       |              | AGING_W   |            |

| XXX10000 10h         |               | CR_OFFSET  V_OFFSET |                   |         |       |              |           | TEM        |

| XXX10001 11h         | Y_OFFSET      |                     |                   |         | VM_   |              | SHP_F0    | CD_OFF     |

| XXX10010 12h         | SHP_CD * 0    |                     |                   |         | SHF   | _F1          | PRE/      | OVER       |

| XXX10011 13h         | VM_COR VM_F0  |                     |                   |         | VM_   | LMT          |           | DLY        |

| XXX10100 14h         | AKBTIM        |                     |                   |         |       | *            | BLK_OFF   | AKBOFF     |

| XXX10101 15h         |               | UP_BLK              |                   |         |       | LO_          | BLK       |            |

| XXX10110 16h         |               | V_SIZE              |                   |         |       |              | V_ON      | EW_DC      |

| XXX10111 17h         |               |                     | V_POS             | SITION  |       |              | VSAW      | 0_DCH      |

| XXX11000 18h         |               | V_l                 | LIN               |         |       | S_CORRECTION |           |            |

| XXX11001 19h         |               |                     | H_S               | SIZE    |       | UP_UCP       |           | UCP        |

| XXX11010 1Ah         |               |                     | PIN_              | _AMP    |       | LO_UCP       |           | UCP        |

| XXX11011 1Bh         |               |                     | UP_               | CPIN    |       |              | UP_       | UCG        |

| XXX11100 1Ch         |               |                     | LO_0              | CPIN    |       |              | _         | UCG        |

| XXX11101 1Dh         |               |                     | PIN_F             | PHASE   |       |              |           | VBLK_SW    |